项目说明

该项目仅仅是我个人的一个练手项目,为的是锻炼我的整体架构设计以及算法实现能力。

首先说明,该项目的设计很烂,为了“快速”完成(虽然并不快つ﹏⊂),几乎没有考虑资源的时分复用,几乎就是直译C语言的代码,因此资源消耗很大(7742个LUT)。主要是因为其中的多个定点数除法IP、开方IP,位数比较多,所以资源消耗也多。同时也没有使用流水线的机制,所以效率也不高(主要是由于UART的传输速率限制,算的再快也没用hhhhh)。

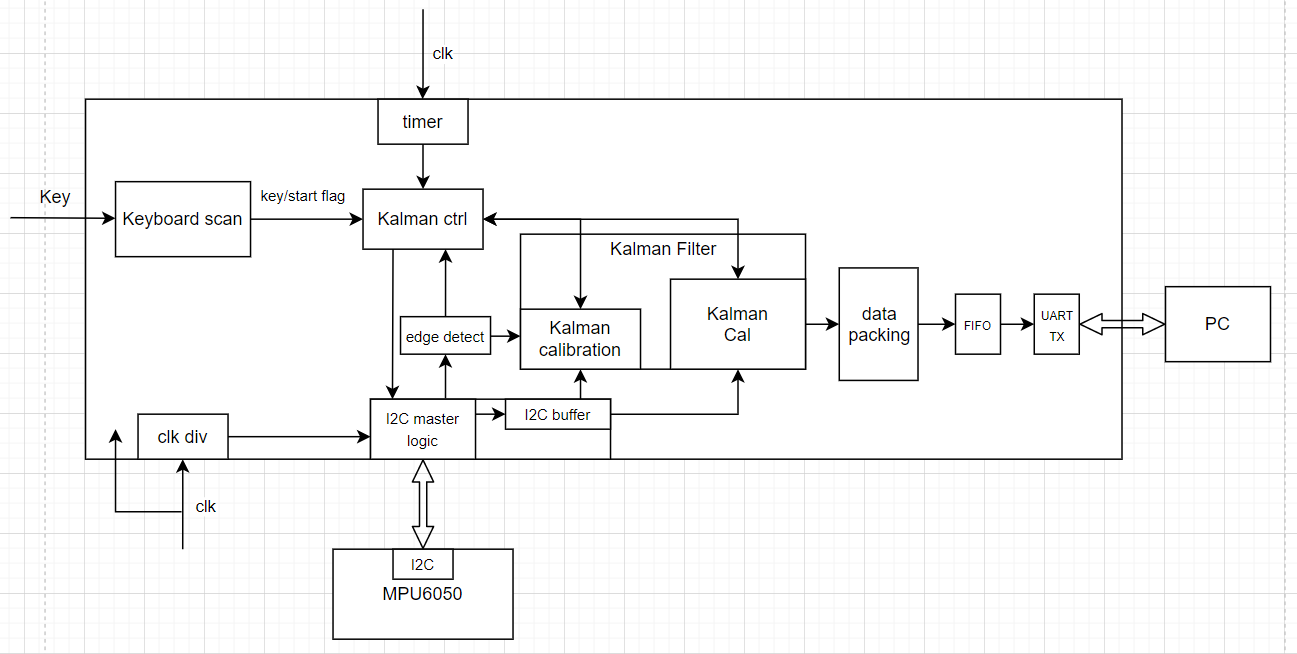

整体架构

项目的整体架构框图如下:

其中所有模块都默认连接了CLK。

模块说明

clk div

给I2C模块的分频

Keyboard scan

扫描按键,用来给Kalman ctrl发送开始信号,复位后按下一次按键以开始实时卡尔曼滤波。

timer

用于控制Kalman ctrl读取I2C数据的速率

edge detect

因为I2C模块的时钟与其他模块不一致,所以需要此模块来检测I2C master控制信号的上升沿。

I2C master logic 和 I2C buffer

实际组成了I2C master模块。

Kalman Ctrl

整个卡尔曼滤波的流程控制模块,整个流程包括一下流程:

- 等待状态(WAIT)

- MPU配置(CONFIG)

- 数据校正(CALIBRATE)

- 滤波计算(CALCULATE)

Kalman calibration 和 Kalman Calculate

共同组成Kalman Filter。

calibration负责数据校正(计算数据偏移),Calculate负责具体的滤波计算

data packing

执行对角度数据的封帧操作,以满足上位机的协议

FIFO 和 UART TX

存储和传输每帧数据给上位机

实际工程中还用了数码管动态显示的模块,只是为了测试用,可有可无。

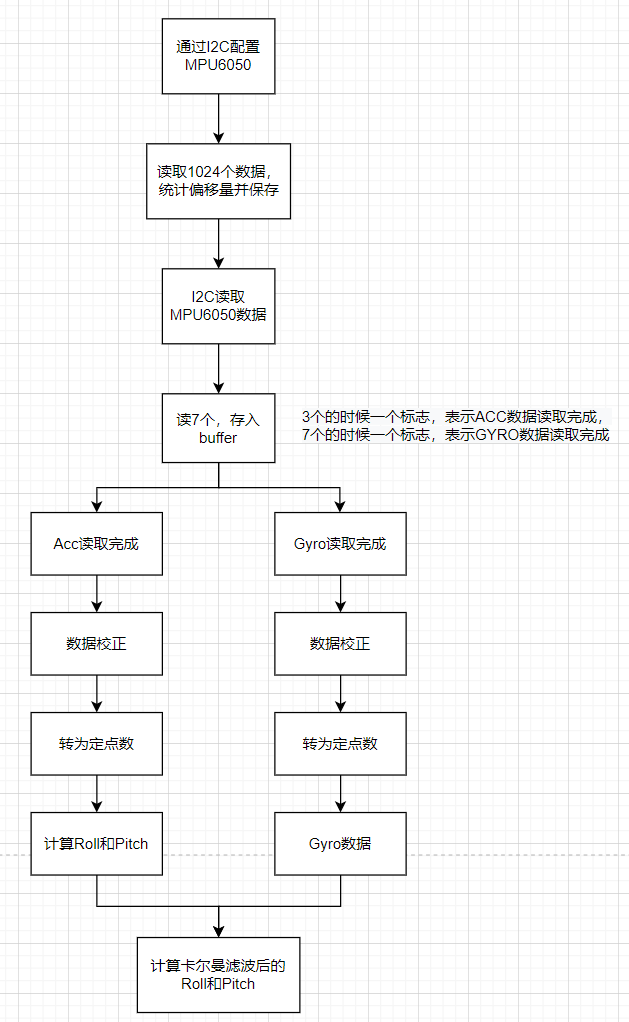

整体计算流程

整体计算流程如下图(很容易理解):

第三方IP使用

I2C IP

首先是I2C的IP,使用的是小脚丫社区开源的IP,本项目在该IP的基础上进行了完善和改进,以完成本项目的目标。

链接:i2c_master_core TEP FPGA开源社区

开方IP

使用的开方IP是vivado中自带的square root IP

除法IP

使用的是vivado自带的Divider Generator IP

UART IP

UART是参考的小脚丫的IP写的,链接:uart_verilog STEP FPGA开源社区

通过该IP,也学到了DDS任意分频的方法👍

CORDIC求反正切IP

参考的是黑金的教程中的IP