Cache是现代CPU中不可缺少的一部分,大大提高了CPU访问数据的速度。

Cache与主存(RAM)的映射关系分为三类:

- 直接相联

- 全相联

- 组相联

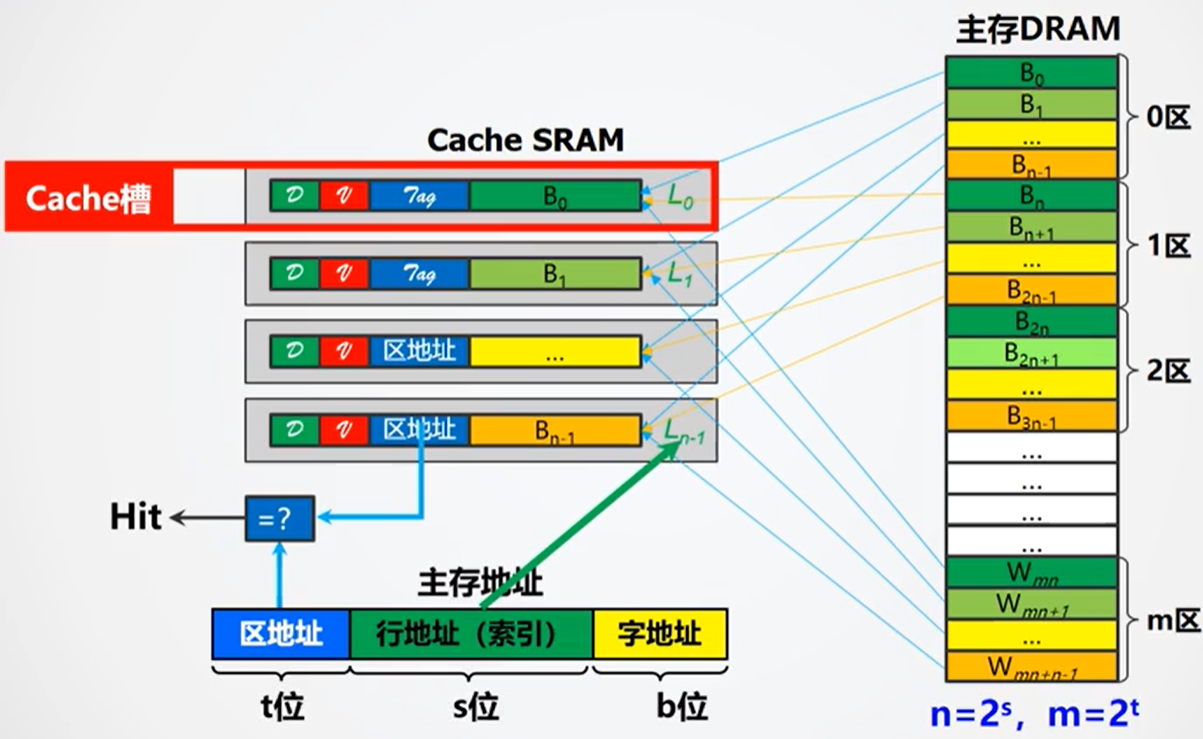

直接相联映射

直接相联就是主存中的一块(行)只能映射到Cache中固定的某一块(行)。

一块(Block)中包含多个字。

同时,主存会根据Cache的块的数量来分区,假设Cache有n块,那么主存中每n块就构成一个区。于是主存地址可以分为3个部分:区地址、行地址、字地址,如下图:

Cache的存储器中,存储一行数据的同时,还会存储区地址以及一些标志位(有效位、一致性Dirty位等),以供在查找数据的时候的判断。

查找的流程如下:

- 根据行地址查找Cache中对应的行

- 根据区地址(标记位TAG)以及一些标志位(有效位 )来判断是否与主存中所要查找的区对应

- 如果TAG一致,则输出该行的数据内容,同时根据字地址来选择最终字的输出

- 如果TAG不一致,则从主存中载入到相应地址的内容到Cache中,再由Cache传输给CPU

这种方法的命中率较低,因为主存中的块只能对应一个Cache块。一个块可能刚进入Cache,就被另一个块给覆盖了。

不过其优点是硬件逻辑简单,成本较低。

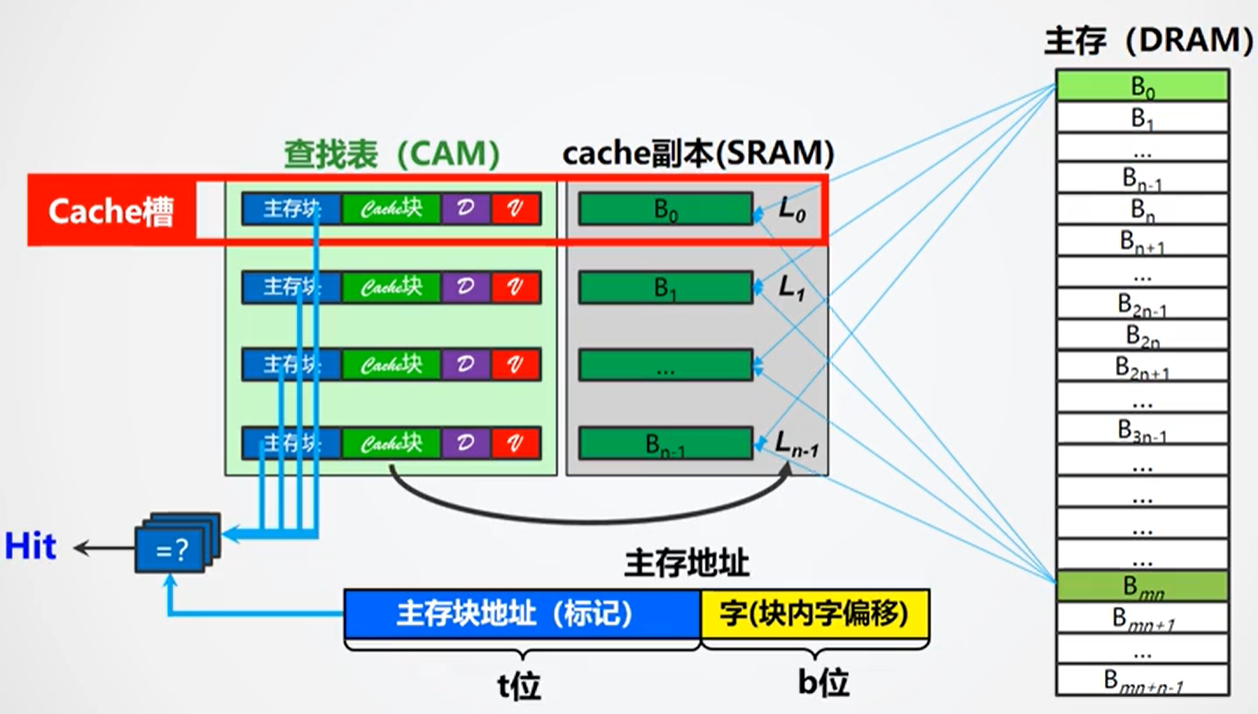

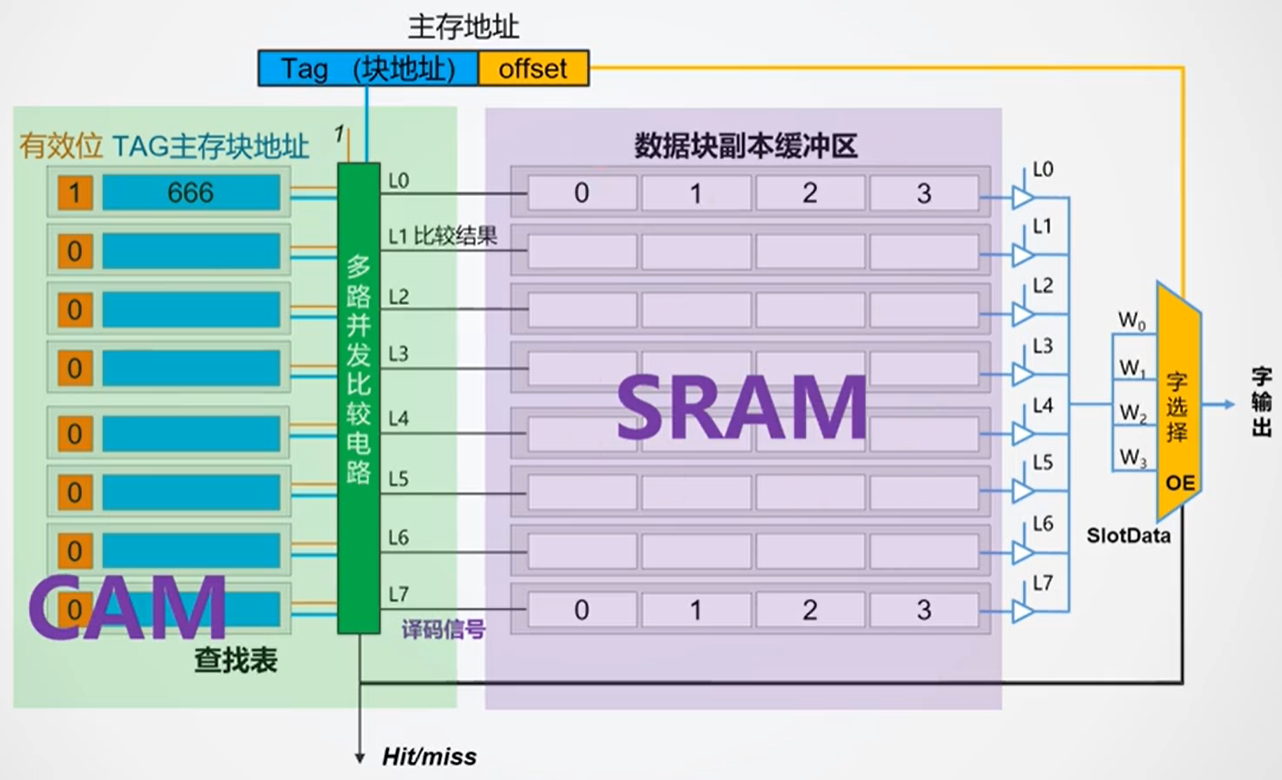

全相联映射

全相联就是主存中的任意一块(行)可以放在Cache中的任意一块(行)中,没有分区的概念。于是贮存地址就只分为两部分:主存块地址(标记部分)、字地址。

由于主存中一个块对应的Cache块地址不确定,所以需要其他的结构来辅助确定,即查找表。查找表的行数与Cache的行数相同,每一行存放着一个主存块地址,一个对应的Cache块地址,以及一些标志位。值得注意的是,查找表(CAM)与Cache是分开存放的,而直接相联中的区地址、标记位等与Cache数据则是一起存放的。

查找流程如下:

- 根据主存块地址在CAM中并行查找Cache中是否存在该块地址

- 若存在,则根据该行对应的Cache块地址直接访问Cache中的相应行,然后根据字地址选择输出的字

- 若不存在,则从RAM中载入相应地址的块到一个空的Cache行中,然后输出

这种方法的命中率比直接相联要高不少,不过其缺点就是硬件开销较大。

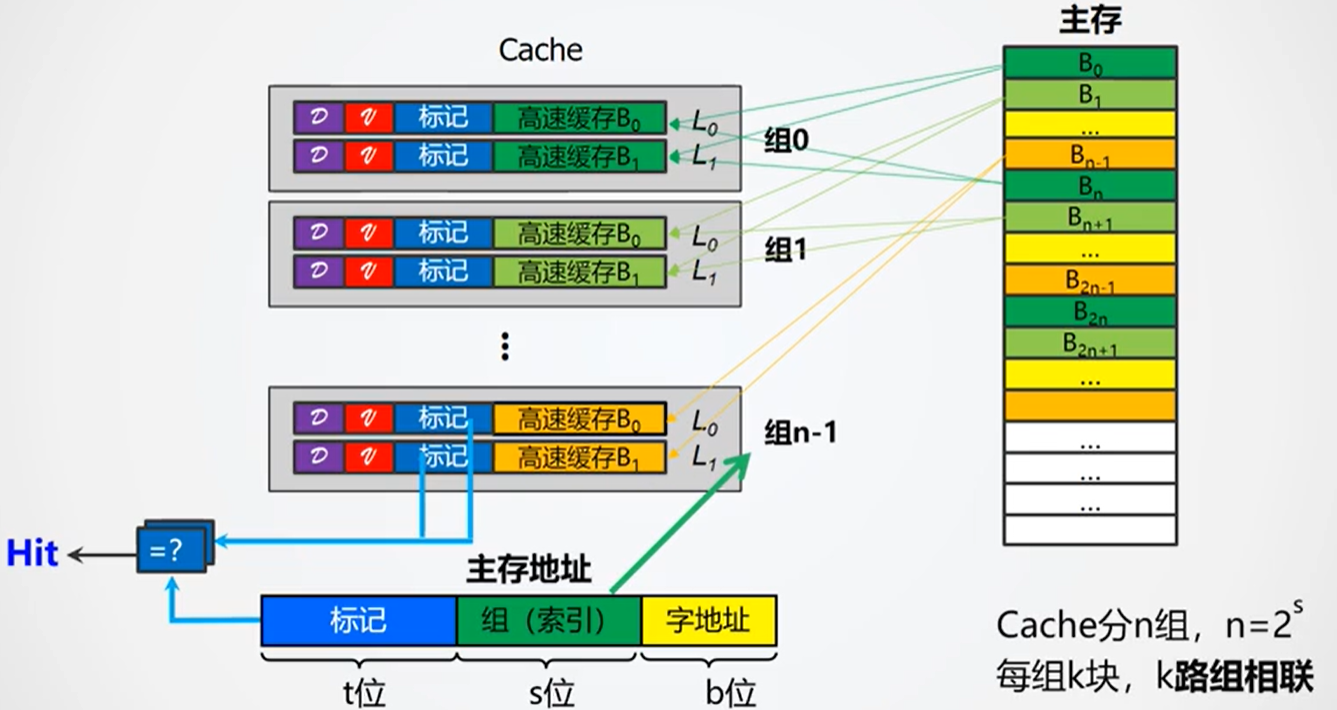

组相联映射

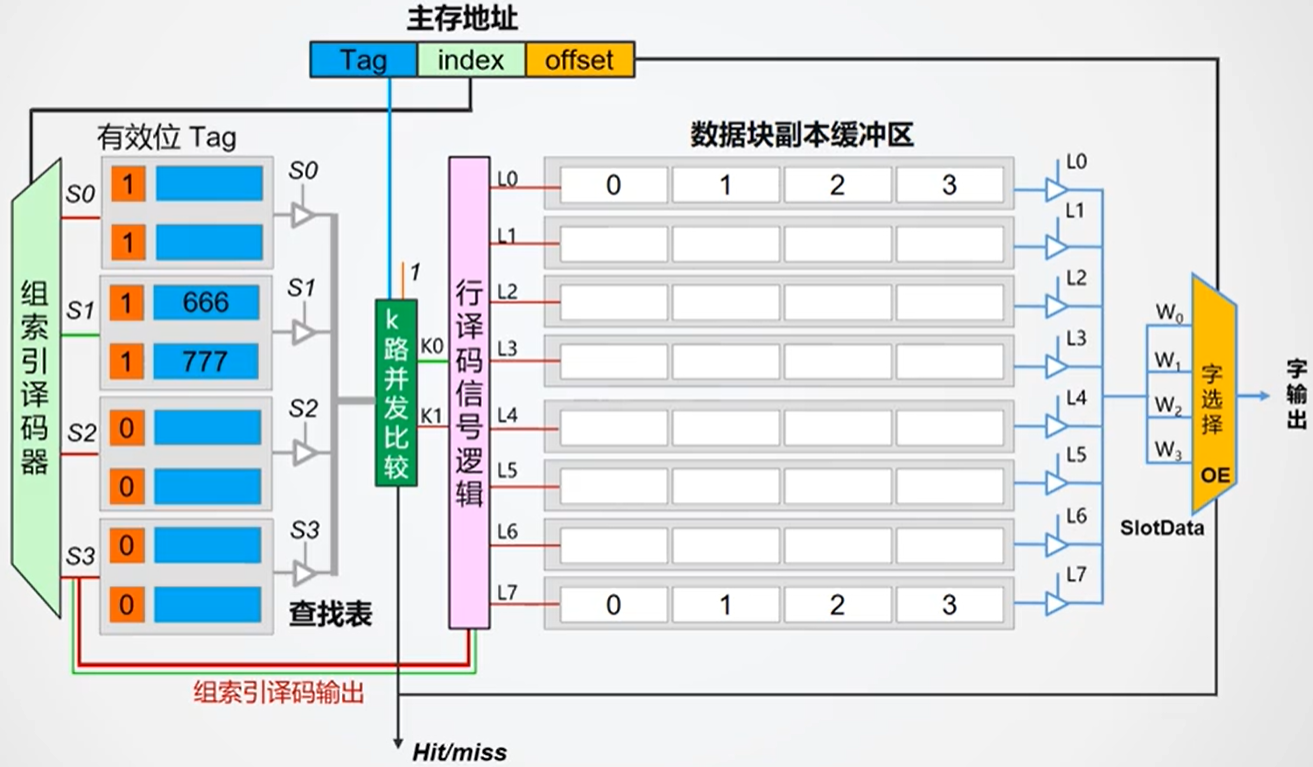

组相联映射结合了直接相联和全相联的特点,首先将Cache分为n组,一组中有k行。主存中也是按照每n行进行分割(类比直接相联的分区),每一行只能进入到相应的Cache组中,但是可以是组中的任意一行(类比全相联)。

每一组中的行数即路数,有k行则被称为k路组相联

于是主存的地址就被分为3个部分:标记字段(区地址)、组地址、字地址。

Cache中一行的组成与直接相联映射类似。

查找的流程如下:

- 首先根据组地址来确定所要查找的组,相应的组信号(S0-3)

- 根据标记字段TAG、有效位确定所要查找的行是否存在于该组中,并输出相应信号(K0、K1…)

- 根据(K0、K1…)以及组信号(S0-3)确定Cache中具体的某一行

- 根据字地址选择最终输出的字

- 若在第2步中,不存在所要查找的行,则从主存中载入,然后再进行步骤3

由组相联的映射机制可知,它结合了直接相联和全相联的特点,是一个比较折中的方案,命中率相比直接相联要高,但是硬件成本也要高一些,相比全相联,其硬件成本较低,但是命中率也要低一些。

由此,我们可以得到一个真理——这个世界上没有什么事物是各个方面都理想的,想要在某方面有所提升,就要付出相应的代价!

同理,想成为大佬就要付出努力!

参考资料:

《计算机硬件系统设计》.华中科技大学计算机学院